Яку функцію виконує озу комп'ютерної техніки. Які функції виконує оперативна пам'ять

Федеральне агентство з освіти

Державне освітня установа

вищої професійної освіти

«Санкт-Петербурзький державний

інженерно-економічний університет»

РЕФЕРАТ

«Оперативна пам'ять ПК, види, призначення та основні характеристики»

з дисципліни «Інформатика»

Керівник А. А. Кантарович

Виконавець В. Калмиков

Група 2601

Санкт-Петербург

2010

Зміст.

1. Оперативна пам'ять. 3

2.Види оперативної пам'яті, їх призначення та основні характеристики. 5

2.1 Статична пам'ять 6

3. Влаштування матриці статичної пам'яті 7

4. Типи статичної пам'яті 8

4.2 Динамічна пам'ять. 9

5. Процедури та функції для роботи з динамічною пам'яттю. 17

Список літератури 21

1.Оперативна пам'ять.

Оперативна пам'ять - це, у вітчизняній науковій термінології, "оперативний пристрій" або ОЗУ, а в західній - RAM, тобто "Random Access Memory" ("пам'ять з довільним доступом"). ОЗП є область тимчасового зберігання даних, за допомогою якої забезпечується функціонування програмного забезпечення. Пам'ять складається з осередків, кожна з яких призначена для зберігання певного обсягу даних, зазвичай одного або чотирьох біт. Чіпи пам'яті працюють синхронно із системною шиною. Комп'ютерна оперативна пам'ять є динамічною (звідси – DRAM або Dynamic RAM) – для зберігання даних у такій пам'яті потрібна постійна подача електричного струму, за відсутності якого осередки спустошуються. Приклад енергонезалежної або постійної пам'яті (ПЗП або ROM - Read Only Memory) пам'яті - флеш-пам'ять, в якій електрика використовується лише для запису та читання, в той час як для зберігання даних джерело живлення не потрібен. Осередки пам'яті в мікросхемах є конденсатори, які заряджаються у разі потреби запису логічної одиниці, і розряджаються при запису нуля. Спустошення пам'яті у разі відсутності електроенергії здійснюється саме за рахунок витоку струмів із конденсаторів. (Рис.1)Рис.1

Принцип роботи оперативної пам'яті можна наступним чином. Оскільки комірки організовані у вигляді двомірної матриці, для отримання доступу до тієї чи іншої комірки необхідно вказати адресу відповідних рядка та стовпця. Для вибору адреси застосовуються імпульси RAS# (Row Access Strobe - стробуючій імпульс доступу до рядка) і CAS# (Column Acess Strobe - стробуючій імпульс доступу до стовпця) при яких рівень сигналу (точніше, напруга) змінюється з високого на низький. Ці імпульси синхронізовані з тактуючим імпульсом, тому оперативна пам'ять також називається синхронною (SDRAM). Спочатку подається сигнал активації необхідного рядка, після чого – імпульс RAS#, а потім – CAS#. При операції запису відбувається те саме, за винятком того, що в цьому випадку подається спеціальний імпульс дозволу запису WE # (Write Enable), який також повинен змінитися з високого на низький. Після завершення роботи з усіма осередками активного рядка виконується команда Precharge, що дозволяє перейти до наступного рядка. Існують і інші сигнали, але в контексті цієї статті їх можна не згадувати, щоб невиправдано не ускладнювати матеріал.

Найважливіша характеристика пам'яті, від якої залежить продуктивність - це пропускна здатність, яка виражається як добуток частоти системної шини на обсяг даних, що передаються за кожен такт. У випадку пам'яті SDRAM ми маємо шину шириною 64 біти або 8 байт. Отже, наприклад, пропускна спроможність пам'яті типу DDR333 становить 333 МГц х 8 Байт = 2,7 Гбайта на секунду або 2700 Мбайт на секунду. Звідси, до речі, і інша назва пам'яті - PC2700, за її пропускною здатністю в мегабайтах на секунду. Останнім часом часто використовується двоканальне підключення пам'яті, у якому теоретична пропускна здатність подвоюється. Тобто, у разі двох модулів DDR333 ми отримаємо максимально можливу швидкість обміну даних 5,4 Гбайта/с.

Тим не менш, частота роботи пам'яті і, отже, її теоретична пропускна спроможність є єдиними параметрами, відповідальними за продуктивність. Насправді не менш важливу роль відіграють і латентність пам'яті, тобто значення затримок між подачею команди та її виконанням. Ці значення прийнято називати таймінгами, які виражаються в тактах, що пройшли між надходженням будь-якої команди і її реальним виконанням. Command rate), причому записуються вони зазвичай у цій же послідовності у вигляді 4-4-4-12-(1T) (цифри в даному випадку довільні). Абревіатура tRCD розшифровується як timе of RAS# to CAS# Delay - таймінг затримки між імпульсами RAS# та CAS#. Скорочення tCL означає timе of CAS# Latency - таймінг затримки щодо імпульсу CAS# після подачі команди запису чи читання. tRP - це timе of Row Precharge: таймінг між завершенням обробки рядка та переходу до нового рядка. Значення tRAS (time of Active to Precharge Delay) вважається одним із основних параметрів, оскільки він описує час затримки між активацією рядка та подачею команди Precharge, якою закінчується робота з цим рядком. Нарешті, параметр Command rate означає затримку між командою вибору конкретного чіпа на модулі та командою активації рядка; зазвичай ця затримка становить трохи більше одного-двох тактів.

Загальне правило свідчить: що менше таймінги при одній тактовій частоті, то швидше пам'ять. Понад те, загалом низці випадків швидше виявляється пам'ять із меншими таймінгами, що працює навіть нижчою тактовою частоті. Вся справа в тому, що, як ми вже згадували, оперативна пам'ять працює синхронно із системною шиною, тому пам'ять із частотою, не кратною частоті системної шини та з пропускною спроможністю, що перевищує пропускну спроможність системної шини, ніяких переваг перед дешевшою не має. Наприклад, системна шина сучасних процесорів Pentium 4 працює на частоті 800 МГц, що при ширині шини 64 біт забезпечує максимальну пропускну здатність 6,4 Гбайта в секунду. Оптимальним вибором для таких чіпів є двоканальна пам'ять DDR2 400 з аналогічною пропускною здатністю в ті ж 6,4 Гбайт на секунду. Використання в двоканальному режимі більш дорогих модулів типу DDR2 533/677 реального збільшення у продуктивності навряд чи дасть. Більше того, в інших випадках є сенс знизити робочу частоту таких модулів, але досягти нижчих таймінгів. Це позитивно позначиться на продуктивності - щоб переконатися в цьому, достатньо прогнати різні тестові програми.

2. Види оперативної пам'яті, їх призначення та основні характеристики.

існує багато різних видівоперативної пам'яті, але їх можна підрозділити на дві основні підгрупи - статична пам'ять (Static RAM) і динамічна пам'ять (Dynamic RAM).Ці два типи пам'яті відрізняються, перш за все, різною в корені технологічною реалізацією - SRAM зберігатиме записані дані доти, доки не запишуть нові або не відключать живлення, а DRAM може зберігати дані лише невеликий час, після якого дані потрібно відновити (регенерувати) , інакше вони будуть втрачені.

Розглянемо переваги та недоліки SRAM та DRAM:

Пам'ять типу DRAM, через свою технологію, має більшу щільність розміщення даних, ніж SRAM.

DRAM набагато дешевше за SRAM, але остання, продуктивніша і надійніша, оскільки завжди готова до зчитування.

2.1 Статична пам'ять

Статична пам'ять або SRAM (Statistic RAM) є найбільш продуктивним типом пам'яті. Мікросхеми SRAM застосовуються для кешування оперативної пам'яті, в якій використовуються мікросхеми динамічної пам'яті, а також для кешування даних в механічних пристроях зберігання інформації, блоках пам'яті відеоадаптерів і т. д. Фактично, мікросхеми SRAM використовуються там, де необхідний обсяг пам'яті не дуже великий, але високі вимоги до швидкодії, а якщо так, то виправдано використання дорогих мікросхем. У персональних комп'ютерах з процесорами, які не мали інтегрованої на кристалі кеш-пам'яті другого рівня, завжди використовувалися мікросхеми SRAM зовнішнього кешу. Для здешевлення системних плат та можливості їх модернізації виробники системних плат з процесорами 486 та перших поколінь Pentium встановлювали спеціальні ліжечка (роз'єми для мікросхем з DIP-корпусом), в які можна було встановлювати різні мікросхеми SRAM, що відрізняються як за швидкодією та обсягом пам'яті, так і різною розрядністю. Для конфігурування пам'яті на системній платі передбачався набір джамперів. Для довідки прямо на системній платі фарбою наносилася інформація про встановлення джамперів, наприклад, як показано в таблиці (у колонках JS1 і JS2 вказані номери контактів, які треба замкнути перемичками).Приклад таблиці конфігурування кеш-пам'яті на системній платі:

| Size | SRAM | JS1 | JS2 |

| 256 К | 32x8 | 1-2 | 1-2 |

| 512 К | 64x8 | 2-3 | 1-2 |

| 1 М | 128x8 | 2-3 | 2-3 |

3. Влаштування матриці статичної пам'яті

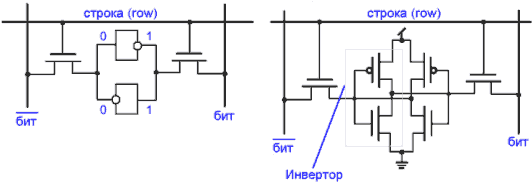

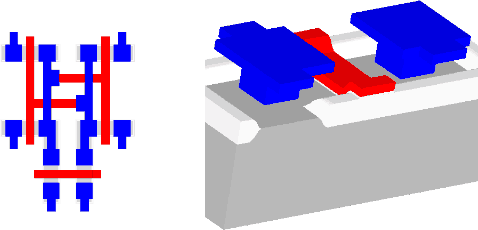

Подібно до осередків динамічної, тригери об'єднуються в єдину матрицю, що складається з рядків (row) і стовпців (column), останні з яких так само називаються бітами (bit).На відміну від комірки динамічної пам'яті, для керування якої достатньо всього одного ключового транзистора, комірка статичної пам'яті управляється як мінімум двома. Це не видасться дивним, якщо згадати, що тригер, на відміну від конденсатора, має окремі входи для запису логічного нуля та одиниці відповідно. Таким чином, на комірку статичної пам'яті витрачається цілих вісім транзисторів (див. рис.2) - чотири йдуть, власне, на сам тригер і ще два - на керуючі засувки.

Мал. 2. Пристрій 6-транзистроного одно-портового осередку SRAM-пам'яті

Причому шість транзисторів на комірку - це ще не межа! Існують і складніші конструкції! Основний недолік шести транзисторного осередку полягає в тому, що в кожний момент часу може оброблятися лише один рядок матриці пам'яті. Паралельне читання осередків, розташованих у різних рядках одного і того ж банку неможливе, так само як неможливо і читання одного осередку одночасно із записом іншого.

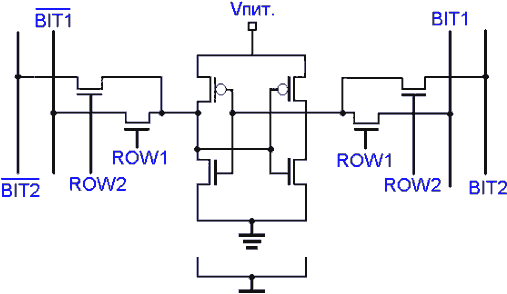

Цього обмеження позбавлена багатопортова пам'ять. Кожна комірка багатопортової пам'яті містить один-єдиний тригер, але має кілька комплектів транзисторів, що управляють, кожен з яких підключений до "своїх" ліній ROW і BIT, завдяки чому різні комірки матриці можуть оброблятися незалежно. Такий підхід набагато прогресивніший, ніж розподіл пам'яті на банки. Адже, в останньому випадку паралелізм досягається лише при зверненні до осередків різних банків, що не здійсненно, а багато портова пам'ять допускає одночасну обробку будь-яких осередків, позбавляючи програміста необхідності вникати особливо її архітектури.

Найчастіше зустрічається двох - портова пам'ять, пристрій комірки якої зображено на рис. 3. (увага! це зовсім та пам'ять яка, зокрема, застосовується у кеші першого рівня мікропроцесорів Intel Pentium). Неважко підрахувати, що для створення одного осередку двох - портової пам'яті витрачається вісім транзисторів. Нехай ємність кеш пам'яті становить 32 Кб, тоді лише на одне ядро піде понад два мільйони транзисторів!

Мал. 3. Пристрій 8-транзистроного двох портового осередку SRAM-пам'яті

Мал. 3. Осередок динамічної пам'яті втілений у кристалі

4. Типи статичної пам'яті

Існує як мінімум три типи статичної пам'яті: асинхронна, синхронна та конвеєрна. Всі вони практично нічим не відрізняються від відповідних типів динамічної пам'яті.Асинхронна статична пам'ять

Асинхронна статична пам'ять працює незалежно від контролера і тому контролер не може бути впевнений, що закінчення циклу обміну збігається з початком чергового тактового імпульсу. В результаті цикл обміну подовжується принаймні на один такт, знижуючи тим самим ефективну продуктивність. "Завдяки" останній обставині, в даний час асинхронна пам'ять практично ніде не застосовується (останніми комп'ютерами, на яких вона ще використовувалися як кеш другого рівня, стали "троячки" - машини, побудовані на базі процесора Intel 80386).

Синхронна статична пам'ять

Синхронна статична пам'ять виконує всі операції одночасно з тактовими сигналами, внаслідок чого час доступу до комірки укладається в один-єдиний такт. Саме на синхронній статичній пам'яті реалізується кеш першого рівня сучасних процесорів.

Конвеєрна статична пам'ять

Конвеєрна статична пам'ять є синхронною. статичну пам'ять, оснащену спеціальними "засувками", що утримують лінії даних, що дозволяє читати (записувати) вміст одного осередку паралельно з передачею адреси іншій.

Також конвеєрна пам'ять може обробляти кілька суміжних осередків за один робочий цикл. Достатньо передати лише адресу першого осередку пакета, а адреси решти мікросхема обчислить самостійно, - тільки встигай подавати (забирати) записування (зчитані) дані!

За рахунок більшої апаратної складності конвеєрної пам'яті час доступу до першого осередку пакета збільшується на один такт, однак, це практично не знижує продуктивності, т.к. всі наступні осередки пакета обробляються без затримок.

Конвеєрна статична пам'ять використовується зокрема у кеші другого рівня мікропроцесорів Pentium-II та її формула виглядає так: 2-1-1-1.

4.2 Динамічна пам'ять.

Всі змінні, оголошені у програмі, розміщуються в одній безперервній області оперативної пам'яті, яка називається сегментом даних. Довжина сегмента даних визначається архітектурою мікропроцесорів 8086 і становить 65536 байт, що може викликати відомі труднощі при обробці великих масивів даних.З іншого боку, обсяг пам'яті ПК (зазвичай щонайменше 640 Кбайт) достатній успішного вирішення завдань із великою розмірністю даних. Виходом із положення може бути використання так званої динамічної пам'яті.

Динамічна пам'ять - це оперативна пам'ять ПК, що надається програмі під час її роботи, за вирахуванням сегмента даних F4 Кбайт), стека (зазвичай 16 Кбайт) та власне тіла програми.

Розмір динамічної пам'яті можна варіювати у межах (див. додаток 1). За замовчуванням цей розмір визначається всією доступною пам'яттю ПК і зазвичай становить не менше 200-300 Кбайт. Динамічна пам'ять - це практично єдина можливість обробки масивів даних великої розмірності. Без динамічної пам'яті важко чи неможливо вирішити багато практичних завдань.

Така необхідність виникає, наприклад, розробки систем автоматизованого проектування (САПР): розмірність математичних моделей, які у САПР, може значно відрізнятися у різних проектах; статичний (тобто на етапі розробки САПР) розподіл пам'яті в цьому випадку, як правило, неможливий. Нарешті, динамічна пам'ять широко застосовується для тимчасового запам'ятовування даних під час роботи з графічними і звуковими засобами ПК.

Динамічне розміщення даних означає використання динамічної пам'яті безпосередньо під час роботи програми. На відміну від цього, статичне розміщення здійснюється компілятором Турбо Паскаля у процесі компіляції програми. При динамічному розміщенні заздалегідь не відомі ні тип, ні кількість даних, що розміщуються, до них не можна звертатися за іменами, як до статичних змінних.

Оперативна пам'ять ПК є сукупністю елементарних осередків для зберігання інформації - байтів, кожен із яких має власний номер. Ці номери називаються адресами, що дозволяють звертатися до будь-якого байта пам'яті.

Турбо Паскаль надає у розпорядження програміста гнучке засіб управління динамічною пам'яттю - звані покажчики. Вказівник - це змінна, яка як своє значення містить адресу байта пам'яті.

У ПК адреси задаються сукупністю двох шістнадцятирозрядних слів, які називаються сегментом та усуненням. Сегмент - це ділянка пам'яті, що має довжину 65536 байт F4 Кбайт) і починається з фізичної адреси, кратного 16 (т. Е. О, 16, 32, 48 і т. д.). Зміщення вказує, скільки байтів від початку сегмента потрібно пропустити, щоб звернутися до потрібної адреси. Адресний простір ПК становить 1 Мбайт (йдеться про так звану стандартну пам'ять ПК; на сучасних комп'ютерах з процесорами 80386 і вище адресний простір становить 4 Гбайт, однак у Турбо Паскалі немає засобів, що підтримують роботу з додатковою пам'яттю; при використанні середовища Borland Pascal with Objects 7.0 така можливість є).

Для адресації в межах 1 Мбайт потрібно 20 двійкових розрядів, які виходять з двох шістнадцятирозрядних слів (сегменту і зміщення) наступним чином (рис. 6.1): вміст сегмента зміщується вліво на 4 розряди, звільнені праві розряди заповнюються нулями, результат Фрагмент пам'яті 16 байт називається параграфом, тому можна сказати, що сегмент адресує пам'ять з точністю до параграфа, а зсув - з точністю до байта. Кожному сегменту відповідає безперервна і окремо адресована область пам'яті. Сегменти можуть йти в пам'яті один за одним без проміжків або з деяким інтервалом, або, нарешті, перекривати один одного. Таким чином, за своєю внутрішньою структурою будь-який покажчик є сукупністю двох слів (даних типу WORD), що трактуються як сег-154.

За допомогою покажчиків можна розміщувати в динамічній пам'яті будь-який із відомих у Турбо Паскалі типів даних. Лише деякі з них (BYTE, CHAR, SHORTINT, BOOLEAN) займають у внутрішньому уявленні один байт, інші - кілька суміжних. Тому насправді покажчик адресує лише перший байт даних. 6.3. Оголошення покажчиків.

Як правило, у Турбо Паскалі покажчик пов'язується з деяким типом даних. Такі покажчики називатимемо типізованими. Для оголошення типізованого покажчика використовується значок л, який міститься перед відповідним типом, наприклад: var pi AInteger; р2: "Real; type PerconPomter = "PcrconRecord; PerconRecord = record Name: String; Job: String; Next: PerconPomter end; Зверніть увагу: при оголошенні типу PerconPointer ми послалися на тип PerconRecord, який попередньо не був оголошений у програмі. Як уже зазначалося, у Турбо Паскалі послідовно проводиться в життя принцип, відповідно до якого перед використанням будь-якого ідентифікатора він має бути описаний. Виняток зроблено лише покажчиків, які можуть посилатися ще не оголошений тип даних. Це не випадково.

Динамічна пам'ять дає можливість реалізувати широко застосовувану деяких програмах організацію даних як списків. Кожен елемент списку має у своєму складі покажчик на сусідній елемент (рис. 6.2), що забезпечує можливість перегляду та корекції списку. Якби в Турбо Паскалі не було цього виключення, реалізація списків була б значно складною. У Турбо Паскалі можна оголошувати покажчик і пов'язувати його у своїй з будь-яким конкретним типом даних. Для цього є стандартний тип POINTER, наприклад: var р: pointer.

1-й елемент списку Вказівник - 2-й елемент списку Останній елемент списку NIL Рис. 6.2. Спискова структура даних Покажчики такого роду називатимемо нешипізованими. Оскільки нетипізовані покажчики не пов'язані з конкретним типом, з їх допомогою зручно динамічно розміщувати дані, структура та тип яких змінюються під час роботи програми.

Як мовилося раніше, значеннями покажчиків є адреси змінних у пам'яті, тому слід очікувати, що значення одного покажчика можна передавати іншому. Насправді, це не зовсім так. У Турбо Паскалі можна передавати значення тільки між покажчиками, пов'язаними з тим самим типом даних. Якщо, наприклад, оголошено змінні pl, p2; "Integer; рЗ: лЯоа1; рр: pointer; то присвоєння pl:= р2; цілком припустимо, у той час як привласнення pl:= рЗ; заборонено, оскільки Р1 і РЗ вказують па різні типиданих. Це обмеження, однак, не поширюється на нетипізовані покажчики, тому ми могли б записати рр: - рЗ, pl: = рр; і цим досягти потрібного результату.

Читач має право поставити запитання, чи варто було вводити обмеження і відразу давати кошти їхнього обходу. Вся справа в тому, що будь-яке обмеження, з одного боку, вводиться для підвищення надійності програм, а з іншого - зменшує потужність мови, робить її менш придатною для якихось застосувань.

У Турбо Паскалі нечисленні винятки щодо типів даних надають мові необхідної гнучкості, але їх використання вимагає від програміста додаткових зусиль і таким чином свідчить про цілком усвідомлену дію.

Виділення та звільнення динамічної пам'яті Вся динамічна пам'ять у Турбо Паскалі розглядається як суцільний масив байтів, який називається купою. Фізично купа розташовується у старших адресах відразу за областю пам'яті, яку займає тіло програми. Початок купи зберігається у стандартній змінній HeapOrg (рис. 6.3), нарешті - у змінній HeapEnd. Поточну межу незайнятої динамічної пам'яті містить змінна Heapptr. Пам'ях під будь-яку змінну, що динамічно розміщується, виділяється процедурою NEW. Параметром звернення до цієї процедури є типізований покажчик. В результаті звернення покажчик набуває значення, що відповідає динамічній адресі, починаючи з якої можна розмістити дані, наприклад: var i, j: "Integer; г: AReal; begin New(i); end."

Після виконання цього фрагмента покажчик 1 набуде значення, яке перед цим мав покажчик купи HEAPPTR, а сам HEAPPTR збільшить своє значення на 2, т. К. Довжина внутрішнього уявлення типу INTEGER, з яким пов'язаний покажчик I, становить 2 байти (на самому У справі це зовсім гак: пам'ять під будь-яку змінну виділяється порціями, кратними 8 байтам - див. разд. 6.7). Оператор new (г); викличе ще раз зміщення покажчика HEAPPTR, але тепер вже на 6 байт, тому що така довжина внутрішнього уявлення типу REAL Аналогічно виділяється пам'ять і для змінної будь-якого іншого типу. Після того, як покажчик придбав деяке значення, тобто став вказувати на конкретний фізичний байт пам'яті, за цією адресою можна розмістити будь-яке значення відповідного типу. Для цього відразу за вказівником без будь-яких прогалин ставиться значок л, наприклад: i = 2, (В область пам'яті i вміщено значення 2) гл = 2 * pi; (В область пам'яті г вміщено значення 6.28)\

Розташування купи в пам'яті ПК Таким чином, значення, на яке вказує покажчик, т. Е. Власне дані, розміщені в купі, позначаються значком Л, який ставиться відразу за покажчиком. Якщо за вказівником немає значка, то мають на увазі адресу, за якою розміщені дані. Має сенс ще раз задуматися над щойно сказаним: значенням будь-якого покажчика є адреса, а щоб вказати, що йдеться не про адресу, а про ті дані, які розміщені за цією адресою, за вказівником ставиться Л. Якщо ви чітко усвідомите це, у вас не буде проблем під час роботи з динамічною пам'яттю. Динамічно розміщені дані можна використовувати в будь-якому місці програми, де це допустимо для констант і змінних відповід- відповідного типу, наприклад: гЛ:<* sqr (rA) + \Л - 17; Разумеется, совершенно недопустим оператор г:= sqr(rA) + iA - 17; т. к. указателю r нельзя присвоить значение вещественного выражения. Точно так же недопустим оператор гл:= sqr (г) ; поскольку значением указателя r является адрес, и его (в отличие от того значения, которое размещено по этому адресу) нельзя возводить в квадрат. Ошибочным будет и такое присваивание: =х; 158 Ядро Турбо Паскаля т. к. вещественным данным, на которые указывает R, нельзя присвоить значение указателя (адрес).

Динамічну пам'ять можна не лише забирати з купи, а й повертати назад. Для цього використовується процедура DISPOSE. Наприклад, оператори disposed); dispose(i); повернуть у купу 8 байт, які раніше були виділені покажчикам 1 і R (див. вище). Зазначимо, що процедура dtspose (PTR) не змінює значення покажчика PTR, лише повертає до купу пам'ять, раніше пов'язану з цим покажчиком. Однак повторне застосування процедури до вільного покажчика призведе до виникнення помилки періоду виконання. Вказівник, що звільнився, програміст може позначити зарезервованим словом NIL. Чи позначений будь-який покажчик чи ні, можна перевірити наступним чином: const р: 4lGal = NIL; begin if p = NIL then new(p); dispose(p); p: NIL; end. Жодні інші операції порівняння над покажчиками не дозволені. Наведений вище фрагмент ілюструє кращий спосіб оголошення покажчика як типізованої константи (див. розділ 7) з одночасним присвоєнням йому значення NIL. Слід врахувати, що початкове значення покажчика (при його оголошенні розділ змінних) може бути довільним. Використання покажчиків, яким не надано значення процедурою NEW або іншим способом, не контролюється системою та може призвести до непередбачуваних результатів.

і т.д.................

Які функції виконує оперативна пам'ять?

Відповідь майстра:

Оперативна пам'ять виконує функцію тимчасового зберігання даних та команд, які необхідні процесору для виконання певних операцій. Надходження даних до оперативної пам'яті відбувається безпосередньо або через надшвидку пам'ять. Вся інформація зберігається тільки при увімкненому комп'ютері, а після його вимкнення всі дані стираються.

У процесі виконання програми деякі з її найбільш важливих файлів завантажуються в оперативну пам'ять (ОЗП), зберігаючись доти, доки програма буде закрито. Сам процесор безпосередньо виконує ці файли, зберігаючи результати. У пам'яті зберігаються всі коди натиснутих клавіш та величини проведених математичних операцій. Після виконання команди Save все, що знаходиться в ОЗУ, зберігається на жорсткий диск.

Більшість користувачів ПК прагнуть збільшення обсягу оперативної пам'яті, оскільки від нього залежить швидкість роботи всіх завантажених процесів. Це має особливу цінність при запуску ресурсомістких програм, наприклад, ігор або різних графічних редакторів. І, відповідно, що більший обсяг має ОЗУ, то швидкісніший ігровий процес та редагування.

Існує безліч типів оперативної пам'яті. Найчастіше зустрічаються DDR, DDRII і DDRIII, відмінності один від одного яких полягає у частоті передачі даних. Чим частота більша, тим швидше робота. Найповільніша з названих – це DDR, а найшвидша – DDR3. Всі ці планки мають різні роз'єми.

У кожному модулі є мікросхеми, які підключаються до системної плати. Ці модулі мають різні характеристики і обов'язково мають бути сумісні із системою, в якій використовуються.

ROM - це постійне запам'ятовуючий пристрій, тому користувач не має можливості здійснювати операції запису. DRAM - динамічний пристрій з довільним порядком вибірки. А SRAM являє собою статичну оперативну пам'ять. ROM та DRAM підтримують зберігання даних, але їх не можна змінювати. Тому в них завантажуються програми, які запускають саму систему. ROM можна вважати частиною оперативної пам'яті системи, а частина будь-якої планки має адресний простір для завантаження найважливішого програмного забезпечення.

Окремо від усього оперативна пам'ять це мікросхема. Існують односторонні та двосторонні планки з розташуванням модулів на одній або обох сторонах.

Повнотекстовий пошук:

Головна > Реферат >Інформатика

Федеральне агентство з освіти

Державний освітній заклад

вищої професійної освіти

«Санкт-Петербурзький державний

інженерно-економічний університет»

РЕФЕРАТ

«Оперативна пам'ять ПК, види, призначення та основні характеристики»

з дисципліни «Інформатика»

Керівник А. А. Кантарович

Виконавець В. Калмиков

Група 2601

Санкт-Петербург

2010

1. Оперативна пам'ять. 2

2. Види оперативної пам'яті, їх призначення та основні характеристики. 5

2.1 Статична пам'ять 5

3. Влаштування матриці статичної пам'яті 6

4. Типи статичної пам'яті 8

4.2 Динамічна пам'ять. 9

5. Процедури та функції для роботи з динамічною пам'яттю. 16

Список літератури 21

1. Оперативна пам'ять.

Оперативна пам'ять - це, у вітчизняній науковій термінології, "оперативний пристрій" або ОЗУ, а в західній - RAM, тобто "Random Access Memory" ("пам'ять з довільним доступом"). ОЗП є область тимчасового зберігання даних, за допомогою якої забезпечується функціонування програмного забезпечення. Пам'ять складається з осередків, кожна з яких призначена для зберігання певного обсягу даних, зазвичай одного або чотирьох біт. Чіпи пам'яті працюють синхронно із системною шиною. Комп'ютерна оперативна пам'ять є динамічною (звідси – DRAM або Dynamic RAM) – для зберігання даних у такій пам'яті потрібна постійна подача електричного струму, за відсутності якого осередки спустошуються. Приклад енергонезалежної або постійної пам'яті (ПЗП або ROM - Read Only Memory) пам'яті - флеш-пам'ять, в якій електрика використовується лише для запису та читання, в той час як для зберігання даних джерело живлення не потрібен. Осередки пам'яті в мікросхемах є конденсатори, які заряджаються у разі потреби запису логічної одиниці, і розряджаються при запису нуля. Спустошення пам'яті у разі відсутності електроенергії здійснюється саме за рахунок витоку струмів із конденсаторів. (Рис.1)

Принцип роботи оперативної пам'яті можна наступним чином. Оскільки комірки організовані у вигляді двомірної матриці, для отримання доступу до тієї чи іншої комірки необхідно вказати адресу відповідних рядка та стовпця. Для вибору адреси застосовуються імпульси RAS# (Row Access Strobe - стробуючій імпульс доступу до рядка) і CAS# (Column Acess Strobe - стробуючій імпульс доступу до стовпця) при яких рівень сигналу (точніше, напруга) змінюється з високого на низький. Ці імпульси синхронізовані з тактуючим імпульсом, тому оперативна пам'ять також називається синхронною (SDRAM). Спочатку подається сигнал активації необхідного рядка, після чого – імпульс RAS#, а потім – CAS#. При операції запису відбувається те саме, за винятком того, що в цьому випадку подається спеціальний імпульс дозволу запису WE # (Write Enable), який також повинен змінитися з високого на низький. Після завершення роботи з усіма осередками активного рядка виконується команда Precharge, що дозволяє перейти до наступного рядка. Існують і інші сигнали, але в контексті цієї статті їх можна не згадувати, щоб невиправдано не ускладнювати матеріал.

Найважливіша характеристика пам'яті, від якої залежить продуктивність - це пропускна здатність, яка виражається як добуток частоти системної шини на обсяг даних, що передаються за кожен такт. У випадку пам'яті SDRAM ми маємо шину шириною 64 біти або 8 байт. Отже, наприклад, пропускна спроможність пам'яті типу DDR333 становить 333 МГц х 8 Байт = 2,7 Гбайта на секунду або 2700 Мбайт на секунду. Звідси, до речі, і інша назва пам'яті - PC2700, за її пропускною здатністю в мегабайтах на секунду. Останнім часом часто використовується двоканальне підключення пам'яті, у якому теоретична пропускна здатність подвоюється. Тобто, у разі двох модулів DDR333 ми отримаємо максимально можливу швидкість обміну даних 5,4 Гбайта/с.

Тим не менш, частота роботи пам'яті і, отже, її теоретична пропускна спроможність є єдиними параметрами, відповідальними за продуктивність. Насправді не менш важливу роль відіграють і латентність пам'яті, тобто значення затримок між подачею команди та її виконанням. Ці значення прийнято називати таймінгами, які виражаються в тактах, що пройшли між надходженням будь-якої команди і її реальним виконанням. Command rate), причому записуються вони зазвичай у цій же послідовності у вигляді 4-4-4-12-(1T) (цифри в даному випадку довільні). Абревіатура tRCD розшифровується як timе of RAS# to CAS# Delay - таймінг затримки між імпульсами RAS# та CAS#. Скорочення tCL означає timе of CAS# Latency - таймінг затримки щодо імпульсу CAS# після подачі команди запису чи читання. tRP - це timе of Row Precharge: таймінг між завершенням обробки рядка та переходу до нового рядка. Значення tRAS (time of Active to Precharge Delay) вважається одним із основних параметрів, оскільки він описує час затримки між активацією рядка та подачею команди Precharge, якою закінчується робота з цим рядком. Нарешті, параметр Command rate означає затримку між командою вибору конкретного чіпа на модулі та командою активації рядка; зазвичай ця затримка становить трохи більше одного-двох тактів.

Загальне правило свідчить: що менше таймінги при одній тактовій частоті, то швидше пам'ять. Понад те, загалом низці випадків швидше виявляється пам'ять із меншими таймінгами, що працює навіть нижчою тактовою частоті. Вся справа в тому, що, як ми вже згадували, оперативна пам'ять працює синхронно із системною шиною, тому пам'ять із частотою, не кратною частоті системної шини та з пропускною спроможністю, що перевищує пропускну спроможність системної шини, ніяких переваг перед дешевшою не має. Наприклад, системна шина сучасних процесорів Pentium 4 працює на частоті 800 МГц, що при ширині шини 64 біт забезпечує максимальну пропускну здатність 6,4 Гбайта в секунду. Оптимальним вибором для таких чіпів є двоканальна пам'ять DDR2 400 з аналогічною пропускною здатністю в ті ж 6,4 Гбайт на секунду. Використання в двоканальному режимі більш дорогих модулів типу DDR2 533/677 реального збільшення у продуктивності навряд чи дасть. Більше того, в інших випадках є сенс знизити робочу частоту таких модулів, але досягти нижчих таймінгів. Це позитивно позначиться на продуктивності - щоб переконатися в цьому, достатньо прогнати різні тестові програми.

2. Види оперативної пам'яті, їх призначення та основні характеристики.

Існує багато різних видів оперативної пам'яті, але їх можна підрозділити на дві основні підгрупи - статична пам'ять (Static RAM) і динамічна пам'ять (Dynamic RAM).

Ці два типи пам'яті відрізняються, перш за все, різною в корені технологічною реалізацією - SRAM зберігатиме записані дані доти, доки не запишуть нові або не відключать живлення, а DRAM може зберігати дані лише невеликий час, після якого дані потрібно відновити (регенерувати) , інакше вони будуть втрачені.

Розглянемо переваги та недоліки SRAM та DRAM:

Пам'ять типу DRAM, через свою технологію, має більшу щільність розміщення даних, ніж SRAM.

DRAM набагато дешевше за SRAM, але остання, продуктивніша і надійніша, оскільки завжди готова до зчитування.

2.1 Статична пам'ять

Статична пам'ять або SRAM (Statistic RAM) є найбільш продуктивним типом пам'яті. Мікросхеми SRAM застосовуються для кешування оперативної пам'яті, в якій використовуються мікросхеми динамічної пам'яті, а також для кешування даних в механічних пристроях зберігання інформації, блоках пам'яті відеоадаптерів і т. д. Фактично, мікросхеми SRAM використовуються там, де необхідний обсяг пам'яті не дуже великий, але високі вимоги до швидкодії, а якщо так, то виправдано використання дорогих мікросхем. У персональних комп'ютерах з процесорами, які не мали інтегрованої на кристалі кеш-пам'яті другого рівня, завжди використовувалися мікросхеми SRAM зовнішнього кешу. Для здешевлення системних плат та можливості їх модернізації виробники системних плат з процесорами 486 та перших поколінь Pentium встановлювали спеціальні ліжечка (роз'єми для мікросхем з DIP-корпусом), в які можна було встановлювати різні мікросхеми SRAM, що відрізняються як за швидкодією та обсягом пам'яті, так і різною розрядністю. Для конфігурування пам'яті на системній платі передбачався набір джамперів. Для довідки прямо на системній платі фарбою наносилася інформація про встановлення джамперів, наприклад, як показано в таблиці (у колонках JS1 і JS2 вказані номери контактів, які треба замкнути перемичками).

Приклад таблиці конфігурування кеш-пам'яті на системній платі:

Зазначимо, що зміною конфігурації кеш-пам'яті займалися лише тоді, коли виходила з ладу будь-яка мікросхема кеш-пам'яті. В інших випадках змінювати положення джамперів не рекомендувалося. Надалі, в міру розробки досконаліших мікросхем SRAM, вони безпосередньо припаювалися на системну плату в кількості 1, 2 або 4 штук. На системних платах, які випускаються нині, мікросхеми SRAM використовуються, переважно, лише кешування вводу/вывода та інших системних функцій.

3. Влаштування матриці статичної пам'яті

Подібно до осередків динамічної, тригери об'єднуються в єдину матрицю, що складається з рядків (row) і стовпців (column), останні з яких так само називаються бітами (bit).

На відміну від комірки динамічної пам'яті, для керування якої достатньо всього одного ключового транзистора, комірка статичної пам'яті управляється як мінімум двома. Це не видасться дивним, якщо згадати, що тригер, на відміну від конденсатора, має окремі входи для запису логічного нуля та одиниці відповідно. Таким чином, на комірку статичної пам'яті витрачається цілих вісім транзисторів (див. рис.2) - чотири йдуть, власне, на сам тригер і ще два - на керуючі засувки.

Мал. 2. Пристрій 6-транзистроного одно-портового осередку SRAM-пам'яті

Причому шість транзисторів на комірку - це ще не межа! Існують і складніші конструкції! Основний недолік шести транзисторного осередку полягає в тому, що в кожний момент часу може оброблятися лише один рядок матриці пам'яті. Паралельне читання осередків, розташованих у різних рядках одного і того ж банку неможливе, так само як неможливо і читання одного осередку одночасно із записом іншого.

Цього обмеження позбавлена багатопортова пам'ять. Кожна комірка багатопортової пам'яті містить один-єдиний тригер, але має кілька комплектів транзисторів, що управляють, кожен з яких підключений до "своїх" ліній ROW і BIT, завдяки чому різні комірки матриці можуть оброблятися незалежно. Такий підхід набагато прогресивніший, ніж розподіл пам'яті на банки. Адже, в останньому випадку паралелізм досягається лише при зверненні до осередків різних банків, що не здійсненно, а багато портова пам'ять допускає одночасну обробку будь-яких осередків, позбавляючи програміста необхідності вникати особливо її архітектури.

Найчастіше зустрічається двох - портова пам'ять, пристрій комірки якої зображено на рис. 3. (увага! це зовсім та пам'ять яка, зокрема, застосовується у кеші першого рівня мікропроцесорів Intel Pentium). Неважко підрахувати, що для створення одного осередку двох - портової пам'яті витрачається вісім транзисторів. Нехай ємність кеш пам'яті становить 32 Кб, тоді лише на одне ядро піде понад два мільйони транзисторів!

Мал. 3. Пристрій 8-транзистроного двох портового осередку SRAM-пам'яті

Мал. 3. Осередок динамічної пам'яті втілений у кристалі